1.7 50fs时钟抖动测量

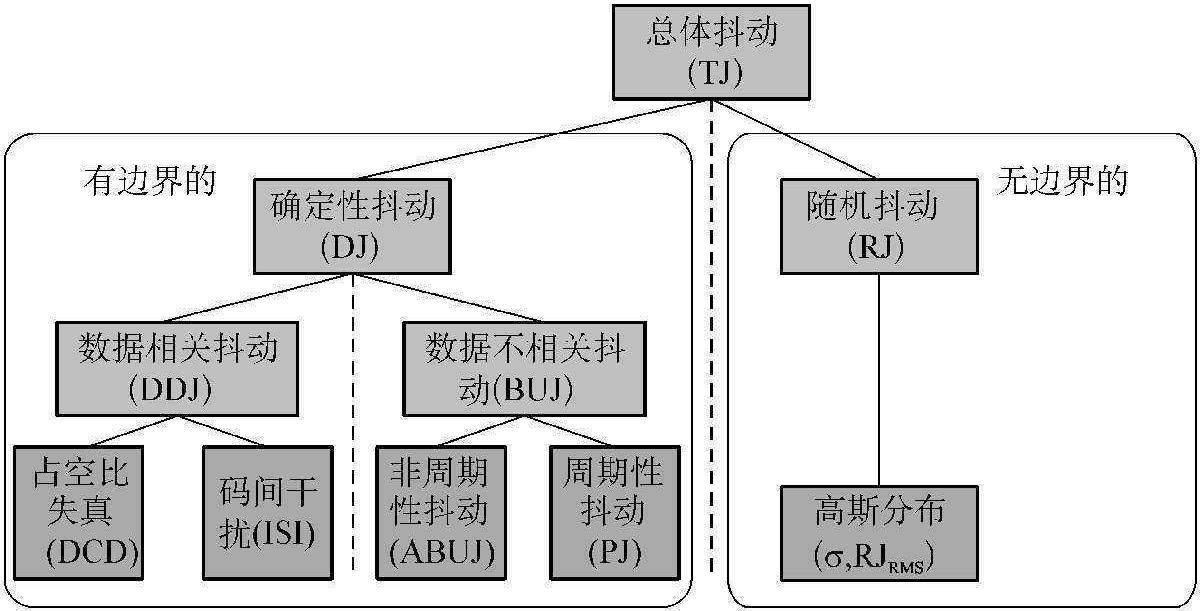

超过10Gbps的SerDes对参考时钟的要求异常苛刻,要求参考时钟的抖动低于100fs,甚至达到50fs的数量级。传统使用示波器的测试方法已经不能满足要求,因为示波器自身的抖动测量本底已经超过100fs数量级。所以测量低于100fs抖动需要采用更高精度的仪器,信号源分析仪或相噪分析仪是一个非常好的选择。

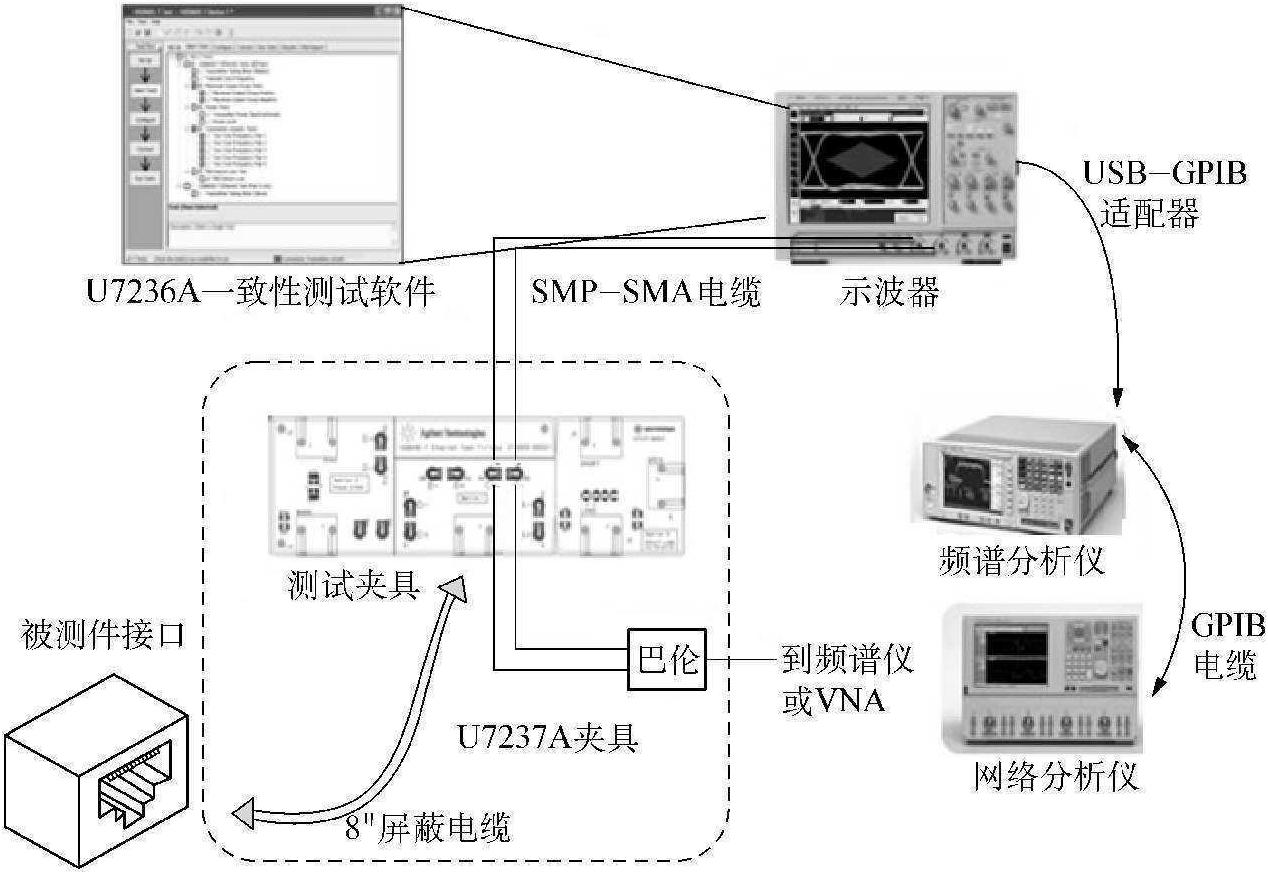

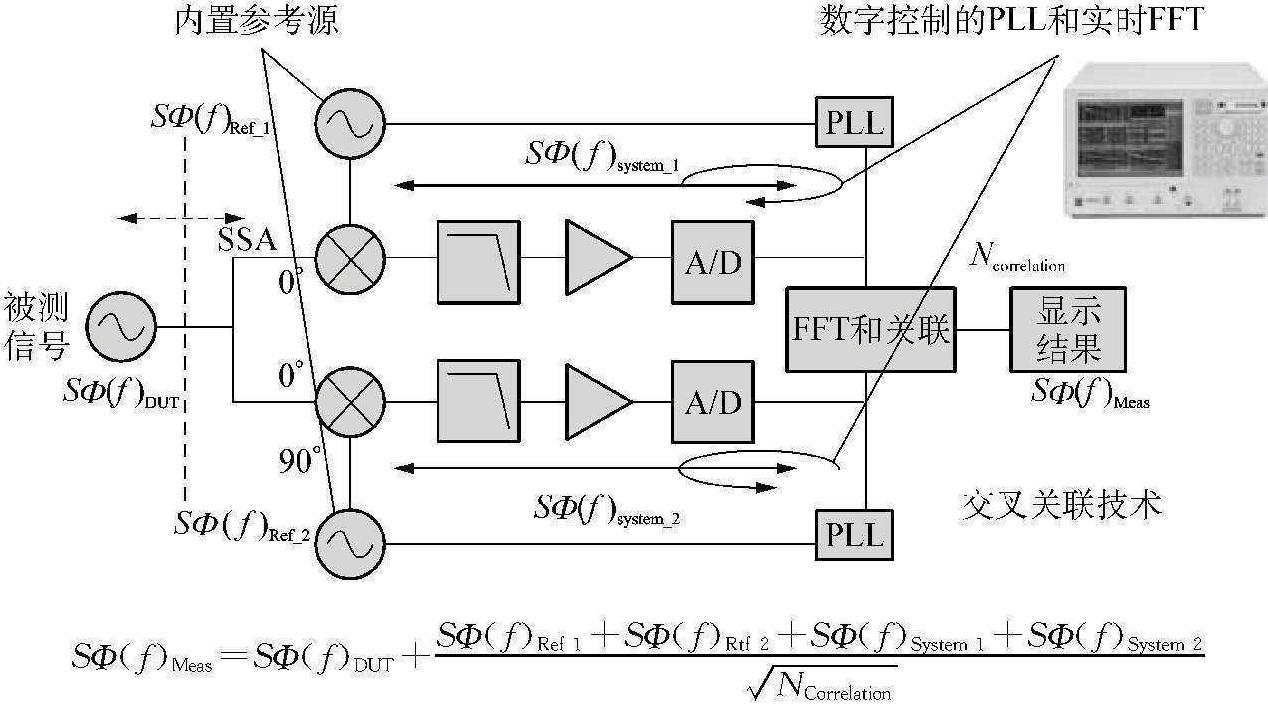

E5052B信号源分析仪是测量晶振、PLL、时钟电路、相位噪声的常用仪器,内部采用独特的设计方法使得测量精度达到50fs数量级,原理框图如图1-11所示。信号源分析仪采用相参接收机的方法降低仪器的本底噪声。信号进入仪器内部后分为两路,每路先用超低相噪本振进行混频,然后通过低通滤波器和放大器 ...... (共589字) [阅读本文]>>

上一篇

上一篇