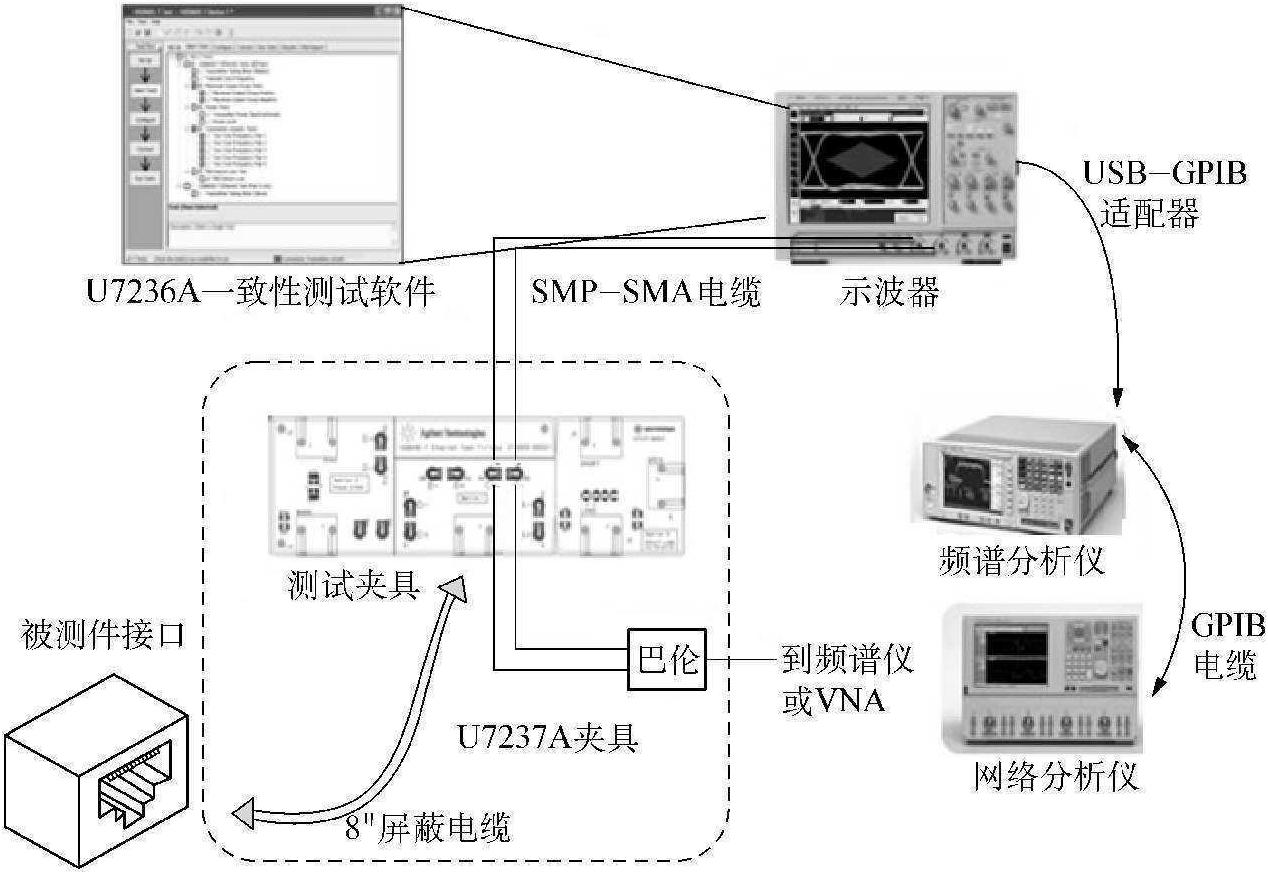

2.2 数字示波器硬件架构

下面以安捷伦的90000A系列数字示波器为例,介绍数字示波器的硬件架构原理。

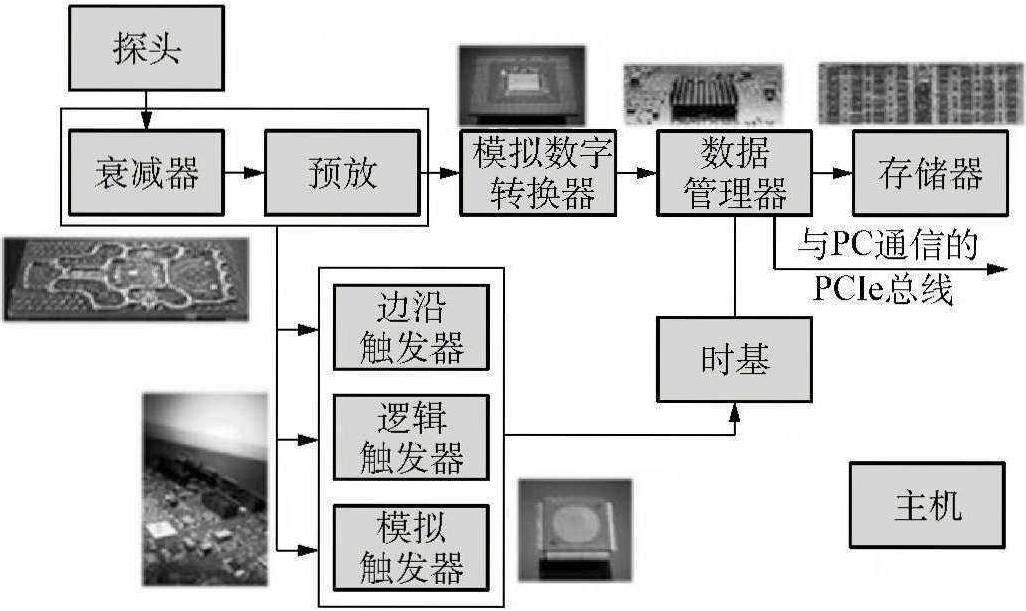

图2-1是数字示波器内部结构图。示波器内部结构主要包括如下几个部分:

(1)信号调理部分:主要由衰减器和放大器组成。

(2)采集和存储部分:主要由模数转换器ADC,内存控制器和存储器组成。

(3)触发部分:主要由触发电路组成。

(4)软件处理部分:由一台计算机组成。

信号进入示波器后,先要进行衰减,再进行放大,这是为什么呢?

原来,衰减器是可调衰减器,当衰减比调节得较大时,让我们能够测试大幅度的信号,当衰减比调节得较小或0dB衰减时,通过放大器的放大作用,使得我们可以测试小幅度的信号。我们平时调节示波 ...... (共1701字) [阅读本文]>>

上一篇

上一篇

扫一扫微信支付

扫一扫微信支付